## International Journal of Ethics in Engineering & Management Education Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 10, October 2018)

# Implementation of Area Efficient High Speed EDDR Architecture

<sup>A</sup>P.SUNITHA, <sup>B</sup>TARRA SEKHAR, <sup>C</sup>E.V.V.GANGA DURGA PRASAD,

<sup>A</sup>Assoc Professor, <sup>B</sup>Asst. Professor, <sup>C</sup>M.Tech Student,

Department of Electronics & Communications, Pragati Engineering College, A.P, India.

<sup>A</sup> sunitha4949@gmail.com, <sup>B</sup> sekhar.tarra@gmail.com, <sup>C</sup> evvgdprasad@gmail.com@gmail.com

Abstract-This project presents an EDDR design, based on the residue-and-quotient (RQ) code, to embed into motion estimation (ME) for video coding testing applications. An error in processing elements (PEs), i.e. key components of a ME, can be detected and recovered effectively by using the EDDR design. The proposed EDDR design for ME testing can detect errors and recover data with an acceptable area overhead and timing penalty. The functional verification and synthesis can be done by Xilinx ISE. That is when compare to the existing design the implemented design area and timing will be reduced.

Index Terms—Area overhead, data recovery, error detection, reliability, residue-and-quotient (RQ) code, Xilinx ISE

#### **I.INTRODUCTION**

Advances in semiconductors, digital signal processing, and communication technologies have made multimedia applications more flexible and reliable. a good example is the h.264 video standard, also known as mpeg-4 part 10 advanced video coding, which is widely regarded as the next generation video compression standard. Video compression is necessary in a wide range of applications to reduce the total data amount required for transmitting or storing video data. Among the coding systems, a me is of priority concern in exploiting the temporal redundancy between successive frames, yet also the most time consuming aspect of coding. Additionally, while performing up to 60%–90% of the computations encountered in the entire coding system, a me is widely regarded as the most computationally intensive of a video coding system.

A ME generally consists of PEs with a size of  $4 \times 4$ . However, accelerating the computation speed depends on a large PE array, especially in high-resolution devices with a large search range such as HDTV. Additionally, the visual quality and peak signal-to-noise ratio (PSNR) at a given bit rate are influenced if an error occurred in ME process. A testable design is thus increasingly important to ensure the reliability of numerous PEs in a ME. Moreover, although the advance of VLSI technologies facilitate the integration of a large number of PEs of a ME into a chip, the logic-per-pin ratio is subsequently increased, thus de-creasing significantly the efficiency of logic testing on the chip. As a commercial chip, it is absolutely necessary for the ME to introduce design for testability (DFT). DFT focuses on increasing the ease of device testing, thus guaranteeing high re-liability of a system. DFT methods rely on reconfiguration of a circuit under test

(CUT) to improve testability. While DFT approaches enhance the testability of circuits, advances in sub micron technology and resulting increases in the complexity of electronic circuits and systems have meant that built-in self-test (BIST) schemes have rapidly become necessary in the digital world. BIST for the ME does not expensive test equipment, ultimately lowering test costs. Moreover, BIST can generate test simulations and analyse test responses without outside support, subsequently streamlining the testing and diagnosis of digital systems. However, increasingly complex density of circuitry requires that the built-in testing approach not only detect faults but also specify their locations for error correcting. Thus, extended schemes of BIST referred to as built-in self-diagnosis and built-in self-correction have been developed recently. While the extended BIST schemes generally focus on memory circuit, testing-related issues of video coding have seldom been addressed. Thus, exploring the feasibility of an embedded testing approach to detect errors and recover data of a ME is of worthwhile interest. Additionally, the reliability issue of numerous PEs in a ME can be improved by enhancing the capabilities of concurrent error detection (CED). The CED approach can detect errors through conflicting and undesired results generated from operations on the same operands. CED can also test the circuit at full operating speed without interrupting a system. Thus, based on the CED concept, this work develops a novel EDDR architecture based on the RQ code to detect errors and recovery data in PEs of a ME and, in doing so, further guarantee the excellent reliability for video coding testing applications. The rest of this paper is organized as follows. Section II describes the mathematical model of RQ code and the corresponding circuit design of the RQ code generator (RQCG). Section III then introduces the proposed EDDR architecture, fault model definition, and test method. Next, Section IV evaluates the performance in area overhead, timing penalty, through put and reliability analysis to demonstrate the feasibility of the proposed EDDR architecture for ME testing applications. Conclusions are finally drawn in Section V.

#### II.RO CODE GENERATION

Coding approaches such as parity code, Berger code, and residue code have been considered for design applications to detect circuit errors. Residue code is generally separable arithmetic codes by estimating a residue for data and appending it to data. Error detection logic for operations is

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 10, October 2018)

typically derived by a separate residue code, making the detection logic is simple and easily implemented. For instance, assume that N denotes an integer,  $N_1$  and  $N_2$  represent data words, and m refers to the modulus. A separate residue code of interest is one in which N is coded as a pair  $(N|N|_m)$ . Notably,  $|N|_m$  is the residue of N modulo m. Error detection logic for operations is typically derived using a separate residue code such that detection logic is simply and easily implemented. However, only a bit error can be detected based on the residue code. Additionally, an error can't be recovered effectively by using the residue codes. There-fore, this work presents a quotient code, which is derived from the residue code, to assist the residue code in detecting multiple errors and recovering errors. The mathematical model of RQ code is simply described as follows. Assume that binary data X is expressed as

$$X = \{bn - 1bn - 2 \dots b2b1b0\} = \sum_{j=0}^{n-1} bj2j$$

(1)

The RQ code of X modulo m expressed as  $R=|X|_m Q=[X/m]$ , respectively.

According to the above RQ code expression, the corresponding circuit design of the RQCG can be realized. In order to simplify the complexity of circuit design, the implementation of the module is generally dependent on the addition operation. Additionally, based on the concept of residue code, the following definitions shown can be applied to generate the RQ code for circuit design.

Definition 1:-

$$\begin{split} |N_{1+}N_2|_m = & |N_1|_m + |N_2|_m|_m \\ \text{Definition 2:- Let } N_j = & n_1 + n_2 + \dots \\ & | N_j |_m = & |N_1|_m + |N_2|_m| + \dots + & | n_j |_m|_m \end{split}$$

To accelerate the circuit design of RQCG, the binary data shown in (1) can generally be divided into two parts:

$$X = \sum_{j=0}^{n-1} bj2j$$

$$= (\sum_{j=0}^{n-1} bj2j) + (\sum_{j=0}^{n-1} bj2j - k)2^{k}$$

$$= Y_{0} + Y_{1}2^{k}$$

(4)

Significantly, the value of k is equal to  $\lfloor n/2 \rfloor$  and the data formation of  $Y_0$  and  $Y_1$  are a decimal system. If the modulus m=2k-1, then the residue code of X modulo m is given by

$$R=|X_{m}|$$

$$=|Y_{0}+Y_{1}|_{m}=|Z_{0}+Z_{1}|_{m}=(Z_{0}+Z_{1})\alpha$$

$$(5)$$

$$Q=\frac{x}{m}$$

$$=\frac{Y_{0}+Y_{1}}{m}+Y_{1}=[\frac{Z_{0}+Z_{1}}{m}]+Z_{1}+Y_{2}$$

$$=Z_{1}+Y_{1}+\beta$$

$$(6)$$

Where

$$\alpha(\beta) = 0(1)$$

, if  $Z_0 + Z_1 = m$

$1(0)$ , if  $Z_0 + Z_1 < m$ .

Notably, since the value of  $Y_0 + Y_1$  is generally greater than that of modulus m, the equations in (5) and (6) must be simplified further to replace the complex module operation with a simple addition operation by using the parameters  $Z_0$ ,  $Z_1$ ,  $\alpha$  and  $\beta$ .

Based on (5) and (6), the corresponding circuit design of the RQCG is easily realized by using the simple adders (ADDs). Namely, the RQ code can be generated with a low complexity and little hardware cost.

#### III.PROPOSED EDDR ARCHITECTURE DESIGN

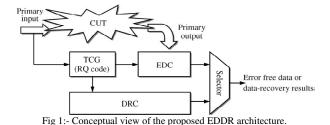

Fig. 1 shows the conceptual view of the proposed EDDR scheme, which comprises two major circuit designs, i.e. error detection circuit (EDC) and data recovery circuit (DRC), to detect errors and recover the corresponding data in a specific CUT. The test code generator (TCG) in Fig. 1 utilizes the concepts of RO code to generate the corresponding test codes for error detection and data recovery. In other words, the test codes from TCG and the primary output from CUT are delivered to EDC to determine whether the CUT has errors. DRC is in charge of re-covering data from TCG. Additionally, a selector is enabled to export error-free data or data-recovery results. Importantly, an array-based computing structure, such as ME, discrete cosine transform (DCT), iterative logic array (ILA), and finite impulse filter (FIR), is feasible for the proposed EDDR scheme to detect errors and recover the corresponding data.

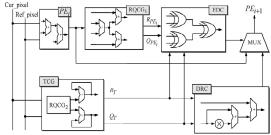

Fig. 2. A specific testing processes of the proposed EDDR architecture.

This work adopts the systolic ME [19] as a CUT to demon strate the feasibility of the proposed EDDR architecture. A ME consists of many PEs incorporated in a 1-D or 2-D array for video encoding applications. A PE generally consists of two ADDs (i.e. an 8-b ADD and a 12-b ADD) and an

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 10, October 2018)

accumulator (ACC). Next, the 8-b ADD (a pixel has 8-b data) is used to estimate the addition of the current pixel (Cur\_pixel) and reference pixel (Ref\_pixel). Additionally, a 12-b ADD and an ACC are required to accumulate the results from the 8-b ADD in order to determine the sum of absolute difference (SAD) value for video encoding applications [20]. Notably, some registers and latches may exist in ME to complete the data shift and storage. Fig. 2 shows an example of the proposed EDDR circuit design for a specific  $PE_i$  of a ME. The fault model definition, RQCG-based TCG design, operations of error detection and data recovery, and the overall test strategy are described carefully as follows.

#### A. Fault Model

The PEs are essential building blocks and are connected regularly to construct a ME. Generally, PEs are surrounded by sets of ADDs and accumulators that determine how data flows through them. PEs can thus be considered the class of circuits called ILAs, whose testing assignment can be easily achieved by using the fault model, cell fault model (CFM). Using CFM has received considerable interest due to accelerated growth in the use of high-level synthesis, as well as the parallel increase in complexity and density of integration circuits (ICs). Using CFM makes the tests independent of the adopted synthesis tool and vendor library. Arithmetic modules, like ADDs (the primary element in a PE), due to their regularity, are designed in an extremely dense configuration.

Moreover, a more comprehensive fault model, i.e. the stuck-at (SA) model, must be adopted to cover actual failures in the interconnect data bus between PEs. The SA fault is a well-known structural fault model, which assumes that faults cause a line in the circuit to behave as if it were permanently at logic "0" (stuck-at 0 (SA0)) or logic "1" [stuck-at 1 (SA1)]. The SA fault in a ME architecture can incur errors in computing SAD values. A distorted computational error (e) and the magnitude of e are assumed here to be equal to SAD,  $\_$ SAD, where SAD, denotes the computed SAD value with SA faults.

#### B. TCG Design

According to Fig. 2, TCG is an important component of the proposed EDDR architecture. Notably, TCG design is based on the ability of the RQCG circuit to generate corresponding test codes in order to detect errors and recover data. The specific  $PE_i$  in Fig. 2 estimates the absolute difference between the Cur\_pixel of the search area and the Ref\_pixel of the current macro block. Thus, by utilizing PEs, SAD shown in as follows, in a macro block with size of  $N \times N$  can be evaluated:-

$$SAD = \sum_{i=0}^{N-1} \sum_{j=0}^{N-1} |X_{ij} - Y_{ij}|$$

$$= \sum_{i=0}^{N-1} \sum_{j=0}^{N-1} |(q_{xij} \cdot m + r_{xij}) - (q_{yij} \cdot m + r_{yij})|$$

(7)

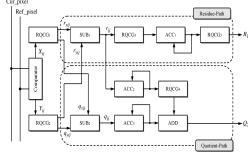

Where  $r_{x\,i\,j}q_{x\,i\,j}$  and  $r_{i\,j}q_{i\,j}$  denote the corresponding RQ code of  $X_{i\,j}$  and  $Y_{i\,j}$  modulo m. Importantly,  $X_{i\,j}$  and  $Y_{i\,j}$  rep-resent the luminance pixel value of Cur\_pixel and Ref\_pixel, respectively. Based on the residue code, the definitions shown in (2) and (3) can be applied to facilitate generation of the RQ code ( $R_T$  and  $Q_T$ ) form TCG. Namely, the circuit design of TCG can be easily achieved (see Fig. 3) by using

$$\begin{split} R_T &= |\sum_{i=0}^{N-1} \sum_{j=0}^{N-1} (X_{ij} - Y_{ij})|_m \\ &= ||(X_{00} - Y_{00)|m| + ||(X_{01} - Y_{01)|m + ... + ||(X_{(N-1)(N-1)} - Y_{(N-1)(N-1))|m|m}} \\ &= ||(q_{x00}.m + r_{x00}) - (q_{y00}.m + r_{y00})|_m + ..... \\ &+ (q_x(_{N-1)(_{N-1}).m + r_x(_{N-1)(_{N-1})}) - (q_y(_{N-1)(_{N-1}).m + r_x(_{N-1})(_{N-1})) - (q_y(_{N-1})(_{N-1})) - (q_y(_{N-1})(_{N-1})(_{N-1})) - (q_y(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1}) - (q_y(_{N-1})(_{N-1})(_{N-1})(_{N-1})) - (q_y(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})(_{N-1})$$

And (9), shown at the bottom of the following page, to derive the corresponding RQ code.

Fig. 3. Circuit design of the TCG.

Fig. 4 shows the timing chart for a macro block with a size of  $4 \times 4$  in a specific  $PE_i$  to demonstrate the operations of the TCG circuit. The data  $n_0$  and  $n_1$  from Cur\_pixel and Ref\_pixel must be sent to a comparator in order to determine the luminance pixel value  $X_{ij}$  and  $Y_{ij}$  at the 1st clock. Notably, if  $X_{ij} \ge Y_{ij}$ , then  $X_{ij}$  and  $Y_{ij}$  are the luminance pixel value of Cur\_pixel and Ref\_pixel, respectively. Conversely,  $X_{ij}$  represents the luminance pixel value of Ref\_pixel, and  $Y_{ij}$  denotes the luminance pixel value of Cur\_pixel when  $X_{ij} < Y_{ij}$ . At the 2nd clock, the values of  $X_0$  and  $Y_{00}$  are generated and the corresponding RQ code  $r_{x00}$

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 10, October 2018)

,  $q_{x00}$ ,  $r_{00}$ ,  $q_{00}$  can be captured by the RQCG and RQCG circuits if the 3rd clock is triggered. Equations (8) and (9) clearly indicate that the codes of  $r_{00}$  and  $q_{00}$  can be obtained by using the circuit of a sub-tracter (SUB). The 4th clock displays the operating results. The modulus value of  $r_{00}$  is then obtained at the 5th clock. Next, the summation of quotient values and residue values of modulo m are proceeded with from clocks 5–21 through the circuits of ACCs. Since a 4 × 4 macron block in a specific  $PE_i$  of a ME contains 16 pixels, the corresponding RQ code ( $R_T$  and  $Q_T$ ) is exported to the EDC and DRC circuits in order to detect errors and recover data after 22 clocks. Based on the TCG circuit design shown in Fig. 4, the error detection and data recovery operations of a specific in a ME can be achieved.

#### C. EDDR PROCESSES

Fig. 2 clearly indicates that the operations of error detection in a specific is achieved by using EDC, which is utilized to compare the outputs between TCG and in order to determine whether errors have occurred. If the values of and/or, then the errors in a specific can be detected. The EDC output is then used to generate a 0/1 signal to indicate that the tested is error-free/errancy. This work presents a mathematical statement to verify the operations of error detection. Based on the definition of the fault model, the SAD value is influenced if either SA1 and/or SA0 errors have occurred in a specific. In other words, the SAD value is transformed to if an error occurred. Notably, the error signal is expressed as

$$E=q_e \cdot m + r_e \tag{10}$$

to comply with the definition of RQ code. Under the faulty case, the RQ code from RQCG of the TCG is still equal to (8) and (9). However,  $R_{PE}$  and  $Q_{PE}$  are changed to (13) and (14) because an error e has occurred. Thus, the error in a specific  $PE_i$  can be detected if and only if (8)  $\neq$  (11) and/or (9)  $\neq$  (12):

$$\begin{split} R_{\text{PEi}} &= |\text{SAD'}|_{\text{m}} \\ &= |\sum_{i=0}^{N-1} \sum_{j=0}^{N-1} (X_{ij} - Y_{ij}) + e|_{\text{m}} \\ &= {}_{\parallel} r_{00 \mid \text{m}} + |r_{01 \mid \text{m}} + ..... + |r_{(N-1)}(N_{N-1})|_{\text{m}} + |r_{e \mid \text{m}} \mid_{\text{m}} \end{split} \tag{11}$$

(12)

$$\begin{split} Q_{\text{PEi}} &= \frac{|\text{SAD'}|}{m} \\ &= \frac{\sum_{i=0}^{N-1} \sum_{j=0}^{N-1} (\text{X}ij - \text{Y}ij) + e}{m} \\ &= q_{00} + q_{01} + \dots + r(N-1)(N-1)) + q_{e+} \quad [ \quad \frac{\text{r00+ r01+.....+ r(N-1)(N-1)) + re}}{m} \end{split}$$

During data recovery, the circuit DRC plays a significant role in recovering RQ code from TCG. The data can be recovered by implementing the mathematical model as

SAD=m x Q<sub>t</sub> + R<sub>t</sub>

=

$$(2^{j}-1)$$

x Q<sub>t</sub> + R<sub>t</sub>

=  $2^{j}$  x Q<sub>t</sub> - Q<sub>t</sub> + R<sub>t</sub> (13)

#### Definitio 1:

|   | 0         | 1   | 2   | 3   |   | 0         | 1 | 2 | 3 |  |

|---|-----------|-----|-----|-----|---|-----------|---|---|---|--|

| 0 | 128       | 128 | 64  | 255 | 0 | 1         | 1 | 2 | 3 |  |

| 1 | 128       | 64  | 255 | 64  | 1 | 1         | 2 | 3 | 4 |  |

| 2 | 64        | 255 | 64  | 128 | 2 | 2         | 3 | 4 | 5 |  |

| 3 | 255       | 64  | 128 | 128 | 3 | 3         | 4 | 5 | 5 |  |

| , | Cur_pixel |     |     |     |   | Ref_pixel |   |   |   |  |

Fig. 5. Example of pixel values.

To realize the operation of data recovery in (13), a Barrel shift and a corrector circuits are necessary to achieve the functions of  $(2^j \times Q_T)$  and  $(Q_T + R_T)$ , respectively. Notably, the proposed EDDR design executes the error detection and data recovery operations simultaneously. Additionally, error-free data from the tested  $PE_i$  or the data recovery that results from DRC is selected by a multiplexer (MUX) to pass to the next specific  $PE_{i+1}$  for subsequent testing.

#### D. Numerical Example

A numerical example of the 16 pixels for a 4  $\times$  4 macro block in a specific  $PE_i$  of a ME is described as follows. Fig. 5 presents an example of pixel values of the Cur\_pixel and Ref\_pixel. Based on (7), the SAD value of the 4  $\times$  4 macro block is

$$SAD = \sum_{i=0}^{3} \sum_{j=0}^{3} (X_{ij} - Y_{ij})$$

$$= |X_{00} - Y_{00}| + |X_{01} - Y_{01}| + ... + X_{33} - Y_{33}|$$

$$= (128 - 1) + (128 - 1) + ... + (128 - 5)$$

$$= 2124$$

$$(14)$$

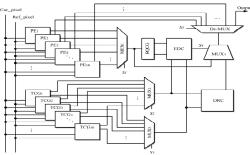

Fig. 6. Proposed EDDR architecture design for a ME.

#### E. Overall Test Strategy

By extending the testing processes of a specific  $PE_i$  in Fig. 2, Fig. 6 illustrates the overall EDDR architecture design of a ME. First, the input data of Cur pixel and

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 10, October 2018)

Ref pixel are sent simultaneously to PEs and TCGs in order to estimate the SAD values and generate the test RQ code  $R_T$ and  $Q_T$ . Second, the SAD value from the tested object  $PE_i$ , which is selected by MUX<sub>1</sub>, is then sent to the ROCG circuit in order to generate  $R_{PE}$  and  $Q_{PE}$  codes. Meanwhile, the corresponding test codes  $R_T$  and  $Q_T$  from a specific  $TCG_i$ are selected simultaneously by MUXs 2 and 3, respectively. Third, the RQ code from  $T C G_i$  and RQCG circuits are compared in EDC to determine whether the tested object  $PE_i$ have errors. The tested object  $PE_i$  is error-free if and only if  $R_{PE} = R_T$  and  $Q_{PE} = Q_T$ . Additionally, DRC is used to recover data encoded by  $TCG_i$ , i.e. the appropriate  $R_T$  and  $Q_T$  codes from  $T C G_i$  are selected by MUXs 2 and 3, respectively, to recover data. Fourth, the error-free data or data recovery results are selected by MUX4. Notably, control signal  $S_4$  is generated from EDC, indicating that the comparison result is error-free  $(S_4 = 0)$  or errancy  $(S_4 = 1).$

#### IV. RESULTS AND DISCUSSION

Extensive verification of the circuit design is performed using the VHDL and then synthesized by the Synopsys Design Compiler with TSMC 0.18-\( \mu \) m 1P6M CMOS technology to demonstrate the feasibility of the proposed EDDR architecture design for ME testing applications.

#### A. Experimental Results

Table I summarizes the synthesis results of area overhead and time penalty of the proposed EDDR architecture. The area is estimated based on the number of gate counts. By considering 16 PEs in a ME and 16 TCGs of the proposed EDDR architecture, the area overhead of error detection, data recovery, and overall EDDR architecture ( $AO_{ED}$ ,  $AO_{DR}$ , and  $AO_{\rm EDDR}$ ) are

$$AO_{ED} = \frac{1779 + 3265 + 16 + 667}{69482 + 13} = 4.92\%$$

$$AO_{DR} = \frac{3265 + 16 + 2376}{69482 + 16} = 4.91\%$$

$$AO_{EDDR} = \frac{1779 + 667 + 3265 + 16 + 2376}{69482 + 16} = 5.13\%$$

(15)

$$(16)$$

The time penalty is another criterion to verify the feasibility of the proposed EDDR architecture. Table I also summarizes the operating time evaluation of a specific  $P E_i$  and each component in the proposed EDDR architecture. The following equations show the time penalty of error detection and data

TABLE I: ESTIMATION OF AREA OVERHEAD AND TIME PENALTY

| i. Estimation of the texter of the time is |        |       |      |         |       |  |  |  |

|--------------------------------------------|--------|-------|------|---------|-------|--|--|--|

| Components                                 | PE     | RQCG  | EDC  | TCG     | DRC   |  |  |  |

| Area 69482<br>(Gate counts)                |        | 1779  | 667  | 3265    | 2376  |  |  |  |

| Operation Time (ns)                        | 973.76 | 10.17 | 6.02 | 1016.56 | 17.99 |  |  |  |

| Area Overhea                               | 5.13   |       |      |         |       |  |  |  |

| Time Penalty                               | 6.24   |       |      |         |       |  |  |  |

$(TP_{\rm ED} \text{ and } TP_{\rm DR})$  operations for a 4 ×4 macro block (a P $E_i$  with 16 pixels):-

$$TP_{ED} = \frac{(1016.56 + 6.02) - 973.76}{973.76} = 5.01\%$$

(18)

$$TP_{ED} = \frac{(1016.56+6.02)-973.76}{973.76} = 5.01\%$$

$$TP_{DR} = \frac{1016.56+17.99-973.76}{973.76} = 6.24\%$$

(19)

Notably, the operating time of the RQCG circuit can be neglected to evaluate T  $P_{\rm E}$   $_{\rm D}$  because TCG covers the operating time of RQCG. Additionally, the error-free/errancy signal from EDC is generated after 1022.58 ns (1016.56 + 6.02). Thus, the error-free data is selected directly from the tested object  $PE_i$  because the operating time of the tested object  $PE_i$  is faster than the results of data recovery from DRC

#### B. Performance Discussion

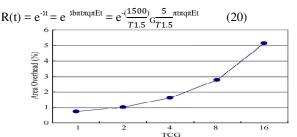

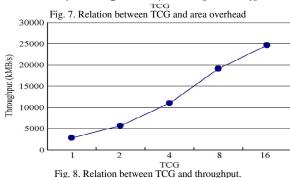

The TCG component plays a major role in the pro-posed EDDR architecture to detect errors and recover data. Additionally, the number of TCGs significantly influences the circuit performance in terms of area overhead and throughput. Figs. 7 and 8 illustrate the relations between the number of TCGs, area overhead and throughput. The area overhead is less than 2% if only one TCG is used to execute; however, at this time, the throughput is extremely small. Notably, the throughput of a ME without embedding the proposed EDDR architecture is about 25 800 kMB/s. Fig. 8 clearly indicates that the throughput is around 25 000 kMB/s, if the proposed EDDR architecture with 16 TCGs is embedded into a ME for testing. Thus, to maintain the same throughput as much as possible, 16 TCGs must be adopted in the proposed EDDR architecture for a ME testing applications. Although the area overhead is increased if 16 TCGs used (see Fig. 7), the area overhead is only about 5.13%, i.e. an acceptable design for circuit testing.

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 10, October 2018)

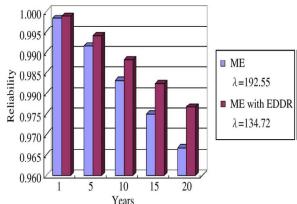

Fig. 9. Failure-rate and reliability analysis

(20) is used to estimate the reliability of the proposed EDDR architecture for ME testing applications, where  $\lambda$  denotes the failure rate; represents the base failure-rate of MOS digital logic; refers to Gate count; (25); (hermetic package); and (ground benign environment). The failure-rate in (20) can be expressed as the ratio of the total number of failures to the total operating time, i.e. failure rate in time (FIT), which represents the number of failures per device hours of accelerated stress tests. Notably, the total operating time, in can be expressed as the year of manufacturing. Since the proposed EDDR architecture is synthesized by using TSMC 0.18 m 1P6M CMOS technology. Fig. 9 clearly indicates that the low failure-rate and high reliability levels can be obtained if the proposed EDDR architecture is embedded into a ME for testing applications.

#### V. CONCLUSION

This work presents EDDR architecture for detecting the errors and recovering the data of PEs in a ME. Based on the RQ code, a RQCG-based TCG design is developed to generate the corresponding test codes to detect errors and recover data. The proposed EDDR architecture is also implemented by using VHDL and synthesized by the Synopsys Design Compiler with TSMC 0.18-\$\mu\$m 1P6M CMOS technology. Experimental results indicate that that the proposed EDDR architecture can effectively detect errors and recover data in PEs of a ME with reason-able area overhead and only a slight time penalty. Throughput and reliability issues are also discussed to demonstrate the satisfactory performance of the proposed EDDR architecture design for ME testing applications.

#### REFERENCES

- Advanced Video Coding for Generic Audiovisual Services, ISO/IEC 14496-10:2005 (E), Mar. 2005, ITU-T Rec. H.264 (E).

- [2] nformation Technology-Coding of Audio-Visual Objects—Part 2: Visual, ISO/IEC 14 496-2, 1999.

- [3] Y. W. Huang, B. Y. Hsieh, S. Y. Chien, S. Y. Ma, and L. G. Chen, "Analysis and complexity reduction of multiple reference frames motion estimation in H.264/AVC," IEEE Trans. Circuits Syst. Video Technol., vol. 16, no. 4, pp. 507–522, Apr. 2006.

- [4] C. Y. Chen, S. Y. Chien, Y. W. Huang, T. C. Chen, T. C. Wang, and L. G. Chen, "Analysis and architecture design of variable block-size motion estimation for H.264/AVC," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 53, no. 3, pp. 578–593, Mar. 2006.

- [5] M. Y. Dong, S. H. Yang, and S. K. Lu, "Design-for-testability techniques for motion estimation computing arrays," in Proc. Int. Conf. Commun., Circuits Syst., May 2008, pp. 1188–1191.

- [6] J. F. Lin, J. C. Yeh, R. F. Hung, and C. W. Wu, "A built-in self-repair design for RAMs with 2-D redundancy," IEEE Trans. Vary Large ScaleIntegr. (VLSI) Syst., vol. 13, no. 6, pp. 742–745, Jun. 2005.

- [7] C. W. Chiou, C. C. Chang, C. Y. Lee, T. W. Hou, and J. M. Lin, "Concurrent error detection and correction in Gaussian normal basis multiplier over GF (2<sup>m</sup>)," IEEE Trans. Comput., vol. 58, no. 6, pp. 851– 857, Jun. 2009.

- [8] S. J. Piestrak, D. Bakalis, and X. Kavousianos, "On the design of selftesting checkers for modified Berger codes," in Proc. IEEE Int. WorkshopOn- Line Testing, Jul. 2001, pp. 153–157.

- [9] D. K. Park, H. M. Cho, S. B. Cho, and J. H. Lee, "A fast motion estimation algorithm for SAD optimization in sub-pixel," in Proc. Int. Symp. Integr. Circuits, Sep. 2007, pp. 528–531.

- [10] J. F. Li and C. C. Hsu, "Efficient testing methodologies for conditional sum adders," in Proc. Asian Test Symp., 2004, pp. 319–324.

- [11] X. Yu, T. Meng, Z. Dai, and X. Yang, "Design and implementation of reconfigurable shift unit using FPGAs," in Proc. IEEE Int. Symp. Pervasive Comput. Applic., Aug. 2006, pp. 543–545.

- [12] X. Li, J. Qin, B. Huang, X. Zhang, and J. B. Bernstein, "A new SPICE reliability simulation method for deep submitcrometer CMOSVLSI circuits," IEEE Trans. Device Mater. Reliable. vol. 6, no. 2, pp. 247– 257.Jun. 2006.