Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 1, January 2018)

# ASynchrobatic Layout Style for Dual-Rail Data-Paths for VLSI Low-Power Design

<sup>1</sup>Lakshmi Kala Pampana

Assistant Professor, Dept. of ECE

Gokaraju Rangaraju Institute of

Engineering and Technology

Bachupally, Hyderabad, Telangana, India

Kala.pampana@gmail.com

<sup>2</sup>Neelam Syamala

Assistant Professor, Dept. of ECE

Marri Laxman Reddy Institute of

Technology and Management

Dundigal, Hyderabad, Telangana, India

Syamu35@gmail.com

<sup>3</sup>Chillarige Gururaja Sesha Talpa Sai Assistant Professor, Dept. of ECE Gokaraju Rangaraju Institute of Engineering and Technology Bachupally, Hyderabad, Telangana, India saicgst@gmail.com

Abstract: In this paper, Asynchrobatic sense is known it's an inimitable low-power technique vogue that mixes the power saving edges of asynchronous logic and adiabatic logic to supply systems whose supremacy dissipation is reduced in many other ways. The terms "Asynchrobatic" could be new words that may be accustomed describe these styles of systems, and springs from the concatenation and shortening of Asynchronous, adiabatic Logic. This paper introduces the contemplation and speculation behind Asynchrobatic Logic. It initial provides Associate in Nursing introductory background to each underlying parent technologies (asynchronous logic and adiabatic logic). background material continues with an evidence of variety of doable strategies for coming up with complicated data-path cells employed in the adiabatic data-path. Asynchrobatic Logic is then introduced as a relationship between asynchronous and Asynchrobatic buffer manacles, showing that for broad systems, it operates a lot of expeditiously. 2 more-complex sub-systems area unit given, foremost a layout implementation of the substitution boxes from the Two fish cryptography algorithmic program, and second a front-end solely (without parasitic capacitances, resistances) simulation that demonstrates a practical system capable of scheming the best Common divisor (GCD) of a combine of 16-bit unsigned integers, that underneath typical conditions on a zero.35µm method, dead a take a look at vector requiring 24 iterations in two.067µs with an influence consumption of three.257nW.

Keywords: ASWC, VLSI, Logic, CMOS, OBDD, Verilog HDL, GCD, MVL

#### 1. INTRODUCTION

Until quite recently, the ability consumption of VLSI computation devices had not been the key limiting considers enhancements and advances in electronics technology. Computers were static, powered by mains electricity, and even the foremost power hungry silicon chip of a PC may well be cooled employing a fan-assisted heat-sink. Current processors will consume 140W, drawing over 100A of current within the method [9] but, the increase of moveable client physics, present computing devices [3], and constituted or wearable bio-medical physics means power economical computation has become a lot of vital in wide deployed technologies, instead of being confined to niche and specialist areas. Also, because the dimensions of CMOS technologies have contracted, in order that for micro millimetre technologies the thickness of the gate nonconductor could be a denumerable variety of atoms [7], ancient power reduction techniques like

voltage scaling have ceased to be as effective, and new problems like source-drain discharge and even gate discharge became important sources of power dissipation.

Depending upon the appliance, there area unit varied strategies that may be accustomed scale back the ability consumption of VLSI circuits, these will vary from low-level measures primarily based upon elementary physics, like employing a lower power provide voltage or mistreatment high threshold voltage transistors; to high-level procedures like clock-gating otherwise power-down modes. The 2 that motivated this investigation were asynchronous logic [9] & [1] and adiabatic logic [2]. These 2 technologies are combined to make Associate in Nursing Asynchronous, adiabatic Logic methodology, known as Asynchrobatic Logic [4], which is that, the subject of this thesis. The name springs as a concatenation and shortening of Asynchronous, adiabatic Logic.

Although celebrated from terribly early within the history of computation, asynchronous logic [5] has till recently remained a lot of a topic of educational analysis than industrial interest. However, in applications like RF-powered good cards, asynchronous implementations of microprocessors usually employed in embedded applications have found a commercially helpful role [Spar01]. one amongst the properties of asynchronous systems that build them helpful in these applications area unit that circuits embody a intrinsic insensitiveness to variations in power provide voltage, with a lower voltage leading to slower operation instead of the practical failures that will be seen if ancient synchronous systems were used. Another major advantage is that the proven fact that once Associate in Nursing asynchronous system is idle there'll be no ticking clock signals, whereas in synchronous systems, these clock signals area unit propagated throughout the whole system and convert energy to heat, typically while not playing any helpful computations.

Adiabatic logic could be a newer space of low-power analysis [10]. It's centered on problems related to the natural philosophy of computation. By taking this branch of physics, that typically appearance at mechanical engines, and applying it to computing engines, analysis fields like reversible computation further as adiabatic logic are created. By moving to a computing paradigm that's reversible, energy will be recovered from a computing engine, and reused to perform additional calculations. The analogy of regenerative braking

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 1, January 2018)

could be a exemplar that illustrates this concept within the context of a well-known system. The low-power good thing about adiabatic logic is that energy will be recycled by being keep and reused, therefore reducing the quantity of energy drawn directly from the ability provide. There area unit alternative low-power consequences of mistreatment sure realisations of adiabatic logic, however these area unit implementation specific instead of being directly attributable to the reversible nature of the logic.

#### 2. ASSOCIATE IN NURSING ADIABATIC LOGIC

"Adiabatic" could be a term of Greek origin that has spent most of its history related to classical natural philosophy. It refers to a system during which a transition happens while not energy (usually within the type of heat) being either lost to or gained from the system. Within the context of electronic systems, instead of heat, electronic charge is preserved. Thus, a perfect adiabatic circuit would operate while not the loss or gain of electronic charge. the primary usage of the term "Adiabatic" during this context seems to be traceable back to a paper given in 1992 at the Second Workshop on Physics and Computation [12]. Though Associate in nursing earlier suggestion of the chance of energy recovery was created by flyer wherever in respect to the energy accustomed perform computation, he declared "This energy may in theory be saved and reused" [2].

The introduction to the present section details the etymology of the term "adiabatic logic". During this section, the underlying physics area unit thought of. Thanks to the Second Law of natural philosophy, it's impossible to fully convert energy into helpful work. However, the term "Adiabatic Logic" is employed to explain logic families that might on paper operate while not losses, and therefore the term "Quasi-Adiabatic Logic" is employed to explain logic that operates with a lower power than static CMOS logic, however that still has some theoretical non-adiabatic losses. In each cases, the terminology is employed to point that these systems area unit capable of operative with considerably less power dissipation than ancient static CMOS circuits, that as is shown in equation (1) operates with a Power, P, that's proportional to each the electrical phenomenon load, CL, and therefore the sq. of the Voltage, V.

#### $P \propto CLV2 ---- (1)$

There area unit many vital principles that area unit shared by all of those low-power adiabatic systems. These embody solely turning switches on once there's no voltage across them, solely turning switches off once no current is flowing through them, and employing a power provide that's capable of sick or employment energy within the type of electrical phenomenon. To achieve this, in general, the ability provides of adiabatic logic circuits have used constant current charging (or Associate in Nursing approximation thereto), in distinction to a lot of ancient non-adiabatic systems that have usually used constant voltage charging from a fixed-voltage power provide.

The power providers of adiabatic logic circuits have additionally used circuit components capable of storing energy. Often done mistreatment inductors [Moon96],that store the energy by changing it to magnetic flux, or, as just in case of Asynchrobatic Logic, by mistreatment capacitors, which may directly store electrical phenomenon.

## 3. STYLE STRATEGIES FOR DUAL-RAIL DATA-PATHS

In this chapter the look strategies for adiabatic logic families are going to be thought of. As noted within the introduction, it's all all right having the ability to implement inverters or buffers, and these area unit usually accustomed demonstrate that circuits will be enforced. However, this can be not associate in nursing adequate take a look at, as a result of inverters and buffers aren't able to perform processing. Unless it's doable to style and viably implement a lot of complicated logic functions, a logic family won't have any real-world applications, as luck would have it for Asynchrobatic Logic, there area unit numerous printed style methodologies for Differential Cascode Voltage Switch Logic (DCVSL) circuits [Chu86] & [Karo95], and these will be accustomed expeditiously style any of the adiabatic derivatives of that logic family that area unit employed in the data-paths of Asynchrobatic Logic systems.

## Adiabatic Style Methodologies

The easiest style methodology to explain, perceive or implement is that the one primarily based upon Ordered Binary call Diagrams (OBDD). During this technique, the logic perform to be enforced is delineate as a tree. Bifurcation happens within the same order regardless of that branch is followed, thence the tree being "ordered". Mistreatment OBDD strategies is certain to end in a functioning circuit, however this circuit is also sub-optimal. It's been shown that the optimum OBDD solution(s) depends upon the order during which the variables area unit evaluated. However, for fourinputs, it's doable to use Associate in Nursing thoroughgoing, brute-force search to get the minimum solution(s). This technique reveals the already celebrated result [13] that each one amongst the 65,536 doable functions of 4 inputs (including degenerate functions wherever one or a lot of input variable has no effect) will be enforced mistreatment solely 222 totally different evaluations structures [Harr63], once their input order reworked bypermutation, and/or negation, and their outputs additionally reworked by negation, the flexibility to turn the input order is clear and is accessible in single-rail logic. However, as a result of this can be a dual-rail logic, negation is additionally freely on the market by swapping the declared high and declared low inputs or outputs. This result's clearly of importance if it were desired to alter this style vogue as a trade goods, as this worth ends up in a clearly outlined limit on the specified size of a universal four-input cell library. Although, as are going to be shown later, it's going to be fascinating to incorporate sure functions of over four inputs in any industrial giving.

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 1, January 2018)

Where the OBDD methodology becomes less helpful is with AND-OR structures wherever the tree depth will be reduced. this may be achieved by mistreatment Quine-McClusky strategies, or by applying easy transforms to applicable structures if these area unit found within the style. The enhancements obtained by mistreatment this technique in specific cases area unit such the seven-input AND-OR perform, employed in look-ahead functions, will be enforced with a most depth of 4 gates as will Associate in Nursing eight-way MUX, that has eleven inputs! Free Binary call Diagram (FBDD) strategies enable a lot of freedom than OBDD strategies because the bifurcation could occur in several orders in several branches. However, this will increase the look area that has got to be searched if one desires to seek out Associate in Nursing optimum resolution by brute force. It additionally makes representing the order during which variables area unit evaluated harder. Whereas the dimensions of Associate in Nursing OBDD's search area grows as a factorial of the quantity of inputs, the FBDD area grows quicker.

Table 3.1: Growth of search space for OBDD and FBDD optimizers

| Number of Inputs | OBDD search space | FBDD search space  |

|------------------|-------------------|--------------------|

| (n)              | (n!)              | (n! <sub>⊤</sub> ) |

| 1                | 1                 | 1                  |

| 2                | 2                 | 2                  |

| 3                | 6                 | 12                 |

| 4                | 24                | 576                |

| 5                | 120               | 16,558,880         |

# 4. MODELLING AND SIMULATING ASYNCHROBATIC LOGIC

It is vital to be able to describe, model and simulate Asynchrobatic Logic systems mistreatment Hardware Description Languages (HDLs) gate simulators like SPICE. HDL simulation is vital not solely as a result of they're the trade commonplace, however as a result of it might take an excessive amount of effort and be too fallible to try to right a SPICE simulation of an outsized system. However, in contrast to the bulk of ancient CMOS-based logic systems, Asynchrobatic Logic doesn't perform signalling employing a single wire to represent one bit. a trifle is described on 2 wires, with 3 outlined states, one invalid state and therefore the risk of varied indefinite states at low-level formatting. The outlined states area unit shown in Table half dozen.1 below:

Table 4.1: Dual-rail logic states in Asynchrobatic Logic

| State    | Asserted Low wire | Asserted High wire |

|----------|-------------------|--------------------|

| Inactive | Low Voltage       | Low Voltage        |

| Logic 0  | High Voltage      | Low Voltage        |

| Logic 1  | Low Voltage       | High Voltage       |

| Invalid  | High Voltage      | High Voltage       |

Because of the redundancy within the signalling, additional logic will be accustomed discover sure faults. This can be as a result of if the power-clock is declared and therefore the 2 wires have equal logic values then there's clearly a fault. Once simulated in code mistreatment HDLs, these states will be detected and rumored. In hardware, a similar plan will be extended to fault and integrity checking. this could enable take a look at structures created with XOR or XNOR gates to be used for producing tests, and probably for tamper detection or signal integrity checking. However, these structures would wish to be able to be disabled to stop spare power consumption, and care would be required to avoid short-circuit currents if static CMOS gates were used. As well as getting used for simulation, HDLs will be used for logic synthesis, permitting a style nominal mistreatment Associate in Nursing HDL to be enforced mechanically.

Verilog HDL was chosen because the HDL to use to model Asynchrobatic Logic. Further as physical exercise personal alternative attributable to larger familiarity, this was done as a result of it provides a far better vary of modelling choices than VHDL. Specifically, VHDL lacks switch-level models as Associate in Nursing integral a part of its language specification. Since the selection of HDL will be attributable to philosophical decision-making, each Verilog and VHDL are going to be mentioned.

## 5. LAYOUT STYLE

The layout performed for the initial experiments that valid Asynchrobatic Logic, were performed employing a stickdiagram layout tool, Chipwise. The ensuing cells were neither ideal for re-use nor for automatic placement. Amirante [4] has enforced numerous regeneration adiabatic Logic (PFAL) cells while not recovery devices mistreatment voltaic cell primarily based layout geometries. this could seem to produce the nice layout methodology. However, it might be simple to increase this work to the reversible PFAL circuits delineate in Chapter five, by having a customary cell with its core, central components shaped by the combine of cross-coupled inverters. The PFAL analysis trees would be placed on one facet of this that leaves area on the unused facet for the recovery devices. If the central core and analysis trees were modularised, then it might in all probability be a comparatively easy refers construct closely reticulate reversible logic data-paths. There area unit 2 factors that complicate combination adiabatic logic cells with commonplace CMOS. The primary is that the hot nwells that has got to be unbroken isolated from one another. This can be not a brand new drawback for static CMOS, as similar isolation problems will occur if it's desired to use backbias to devices. The implication is that solely n-wells sharing a similar power-clock will be abutted. The second issue associated with the stopped-up metal layers. In general, commonplace CMOS solely uses layers up to and together with the primary metal layer for routing among a customary cell. thanks to the quantity of dual-rail signals that has got to cross one another, it's necessary to own access to the second metal layer once constructing complicated adiabatic logic gates. Clearly, these layers will be marked as stopped-up for

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 1, January 2018)

automatic tools, however it might build adiabatic logic less appropriate for older CMOS processes with solely 2 metal layers.

The Asynchronous Stepwise Charging (ASWC) controller will clearly be modularised, with the C-element, the heart beat generators, and therefore the intermediate shift stages all being separate elements. this could enable the development of ASWC circuits with Associate in Nursing impulsive variety of steps.

The a lot of complicated asynchronous management structures will be de-escalated into standard units, most of that area unit elements sometimes found in commonplace CMOS cell libraries, thus it mustn't be too tough to travel to layout for these.

One issue that is clear upon visual examination of the layouts is that the quantity of area needed for the dual-rail interconnect. Because the variety of metal layers will increase in fashionable deep sub-micron and micromillimetre processes, this issue mustn't be insurmountable. The layout style additionally suggests that the look could have XT problems. However, as a result of the data-path in Associate in Nursing Asynchrobatic system contains a totally different procedure from that of static CMOS, it's less probably that XT can cause major issues, however any risk of this might be minimised by precluding the utilization of adiabatic logic families while not cross-coupled NMOS devices (like ECRL), and by guaranteeing that the parasitic extraction of layouts is performed to incorporate inter-net, cross-coupled capacitances, and not simply capacitance lumped to ground.

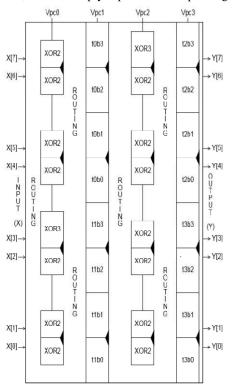

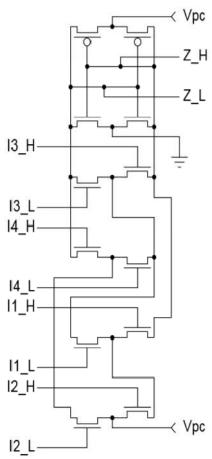

Figure 1: Floor-plan of Twofish q-boxes

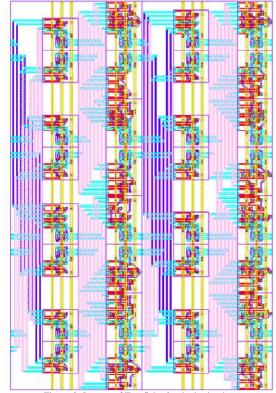

Figure 2: Layout of Twofish q0 substitution box

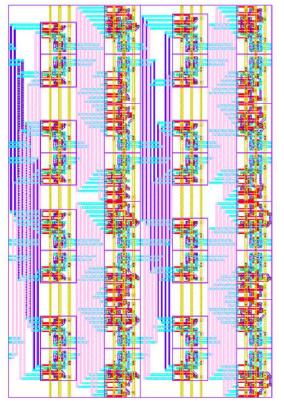

Figure 3: Layout of Twofish q1 substitution box

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 1, January 2018)

## 6. CONCLUSION

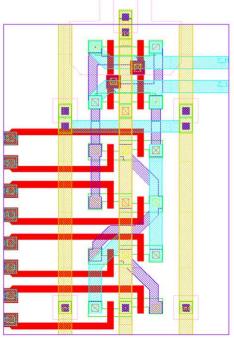

Figure 4: Layout of q1t0b2 cell

Figure 5: q1t0b2 circuit diagram

In the initial four chapters of this thesis, the foundations upon that Asynchrobatic Logic is made are introduced. These area unit adiabatic Logic, Asynchronous Logic, and therefore the style strategies for dual-rail logic. Though the bulk of this material was antecedently celebrated, this introduction extended information by quantifying however the quantity of inputs causes the dimensions of the search area without charge n-ary call Diagrams to extend, together with suggestion doable applications in ambiguous Logic (MVL).

Asynchrobatic Logic has been introduced. It's been shown to be a viable technique for the implementation of novel, low-power, complicated systems. the actual fact that Associate in Nursing operational implementation of the best Common divisor (GCD) algorithmic program may well be created shows that systems capable of playing iteration and call will be enforced. The importance of this can be that it's been shown that these 2 constructs area unit needed to permit structured programming [6]. This suggests that Asynchrobatic Logic may well be accustomed implement at random complicated machine systems. Though the GCD was a netlist solely simulation, the layout implementation of the q-boxes from the Twofish algorithmic program shows that viable physical implementations also can be created.

As well as manufacturing electronic equipment capable of implementing Asynchrobatic Logic, this work has shown that it's doable to model Asynchrobatic Logic mistreatment the Hardware Description Languages (HDLs) Verilog and VHDL. the flexibility to model complicated systems mistreatment a lot of abstract representations is important as a result of playing SPICE simulations would take too long, and any mistakes would be way more tough to find or diagnose.

#### **REFERENCES**

- David John WILLINGHAM, ASYNCHROBATIC LOGIC FOR LOW-POWER VLSI DESIGN, University of Westminster for the degree of Doctor of Philosophy, March 2010

- [2]. David J. Willingham and İzzet Kale, "Asynchronous, quasi-adiabatic (Asynchrobatic) logic for low power very wide data width applications", Proceedings of the 2004 International Symposium on Circuits and Systems (ISCAS 2004), volume 2, pages II:257-260, Vancouver, Canada, 23rd-26th May 2004.

- [3]. David J. Willingham and İzzet Kale, "An Asynchrobatic, Radix-four, Carry Look-ahead Adder", Proceedings of Ph.D. Research in Microelectronics and Electronics (PRIME 2008), pages 105-108, İstanbul, Turkey, 22nd-25th June 2008.

- [4]. David J. Willingham and İzzet Kale, "Using Positive Feedback Adiabatic Logic to implement Reversible Toffoli Gates", Proceedings of NORCHIP 2008, pages 5-8, Tallinn, Estonia, 17th-18th November 2008

- [5]. David J. Willingham and İzzet Kale, "A system for calculating the Greatest Common Denominator implemented using Asynchrobatic Logic", Proceedings of NORCHIP 2008, pages 194-197, Tallinn, Estonia, 17th-18th November 2008.

- [6]. Douglas Adams, "The Hitch-Hiker's Guide to the Galaxy", Pan Books, page 135, October 1979, ISBN: 0-330-25864-8.

- [7]. Advanced Micro Devices Inc., "AMD Family 10h Desktop Processor Power and Thermal Data Sheet", revision 3.18, February 2009. Available via the following URL: http://www.amd.com/.

- [8] E. Amirante, J. Fischer and D. Schmitt-Landsiedel, "Verlustleistungsschwankungen in adiabatischen Schaltungen", ITG-

Website: www.ijeee.in (ISSN: 2348-4748, Volume 5, Issue 1, January 2018)

- Fachbericht 162, "Mikroelektronik für die Informations-technik", Darmstadt, Germany, 20th-21st November 2000, pages 133-138.

- [9]. Ettore Amirante, "Adiabatic Logic in Sub-Quartermicron CMOS Technologies", Shaker Verlag GmbH, Aachen, Germany, 2004. ISBN: 3-8322-3487-X. ISBN13: 9783832-234874.

- [10]. AMI Semiconductor Belgium BVBA, "C035M Design rule manual supplement for analogue option (C035M-A)", DS13337, Revision: 3.0, 7th August 2002

- [11]. AMI Semiconductor Belgium BVBA, "C035M-D Design rule manual", DS13330, Revision: 5.0, 16th January 2003.

- [12]. A. Armah, and A. Jaekel, "An ordering-insensitive methodology for efficient DCVS circuit synthesis", Proceedings of IEEE Canadian Conference on Electrical and Computer Engineering (CCECE'98), volume 1, pages I:49-52, Waterloo, Ontario, Canada, 24th-28th May 1998.

- [13]. M. Arsalan and M. Shams, "Asynchronous Adiabatic Logic", Proceedings of the International Symposium on Circuits and Systems (ISCAS'07), pages 3720-3723, New Orleans, Louisiana, USA, 27th-30th May 2007.

- [14] P. Asimakpoulos and A. Yakovlev, "An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits", Web pages of the 20th UK Asynchronous Forum, Manchester, Great Britain, 1st-2nd September 2008. Available at the following URL: http://intranet.cs.man.ac.uk/apt/async/events/ukforum20/.

- [15] W. C. Athas, N. Tzartzanis, L. "J." Svensson, L. Peterson, H. Li, P. Wang and W.-C. Liu, "AC-1: a clock-powered microprocessor", Proceedings of the 1997 International Symposium on Low Power Electronics and Design (ISLPED'97), pages 328-333, Monterey, California, USA, 18th-20th August 1997.

- [16]. L. "J." Svensson, W. C. Athas and J. G. Koller, "System and method for power-efficient charging and discharging of a capacitive load form a single source", US Patent 5,473,526, 5th December 1995.

- [17]. L. "J." Svensson, W. C. Athas, R. S.-C. Wen, "A sub-CV<sup>2</sup> pad driver with 10ns transition time", Proceedings of IEEE Symposium on Low Power Electronics and Design (ISLPED'96), pages 105-108, Monterey, California, USA, 12th-14th August 1996.

- [18] I. E. Sutherland, "Micropipelines", Communications of ACM 32(6):720-738, January 1989.

- [19]. Nazeih M. Botros, "HDL Programming Fundamentals; VHDL and Verilog", Charles River Media, Massachusetts, USA, 2006, ISBN: 9-781584-508557.

- [20]. Anantha P. Chandrakasan and Robert W. Brodersen, "Low Power Digital CMOS Design", Kluwer Academic Publishers, Massachusetts, USA, 1995, ISBN: 9-780792-395768, Chapter 6 (Lars Svensson, "Adiabatic Switching"), pages 181-218.

- [21]. Anthony J.G. Hey (editor), "Feynman and Computation", Westview Press, USA, ISBN: 978-08133-4039-5.

- [22] Hubert Kaeslin, "Digital Integrated Circuit Design; From VLSI Architectures to CMOS Fabrication", Cambridge University Press, 2008, ISBN: 978-0-521-88267-5.