## International Journal of Ethics in Engineering & Management Education Website: www.ijeee.in (ISSN: 2348-4748, Volume 4, Issue 3, March 2017)

# The Design of High Speed and Low Power Dual Tail Comparator using Power Gating Technique

G. Snehalatha CVR College of Engineering, ECE Dept, Hyderabad, India Email: sneharaj401@gmail.com

Abstract— This paper presents the comparison of proposed double tail comparator with conventional double tail and existing double tail comparator. The low power and high-speed analog to digital converters used are of dynamic regenerative comparators to maximize speed. Presenting different architectures for calculating delay and power consumption in dynamic double tail comparator. The power gating technique is used to design the proposed comparator. By using this technique, delay and power consumption is reduced compared to the conventional double tail comparator and the existing double tail comparator. The important parameters are speed and power consumption. Cadence design tools used to simulate the comparator in the 90nm technology with the supply voltage of 0.6v.

Index Terms- Dynamic latch comparator, speed, power consumption, high speed analog to digital converter.

### **I.INTRODUCTION**

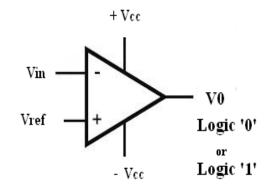

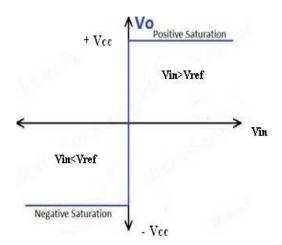

Comparator is a circuit that output is binary information depending upon the comparison of two input voltages here the comparison in between analog voltage and reference voltage. Analog voltage is greater than reference voltage, and then comparator output is logic '1'. comparator output is logic '0', when analog voltage is less than reference voltage. Comparators are effectively used in analog to digital (ADC) converters. In analog to digital conversion process [1], the analog voltage is converted in to samples for getting accuracy. Those samples are given to set of comparators in order to achieve equivalent binary information. The schematic of a voltage comparator shown in Fig 1.Comparator transfer characteristics shown in Fig 2. Comparator truth table shown in Table 1. Comparator applications are analog to digital converters and data receivers. The dynamic latch comparators used in these applications in order to achieve high-speed and low power. Dynamic comparators have no static power consumption because of strong positive feedback. Dynamic latch comparator [3] is suitable for high-speed analog to digital converters (ADC). The first stage of clocked comparator is given to the inputs. Second stage of clocked comparator consists of two cross coupled inverters called regenerative stage. In this stage each inverter input is connected to the other inverter output. The important parameters like speed, power consumption, and transistor count are very important in comparator applications. By using a clocked regenerative structure will get low power and good output swing. When the clock is high (CLK=  $V_{DD}$ )

comparator circuit works in comparison phase. When the clock is low (CLK=0) comparator circuit works in reset phase.

CMOS technology suffers from low supply voltages for designing high speed comparators. Hence, designing high-speed comparators with low supply voltages many techniques are there such as supply boosting [6] methods, techniques employing body driven

Fig 1. Schematic of comparator

Fig 2. Comparator Transfer Characteristics

transistors and current mode designs developed higher supply voltages to meet low supply voltage design challenges. NMOS switches added to the input transistors used to overcome the static power consumption. The regenerative comparator design

Website: www.ijeee.in (ISSN: 2348-4748, Volume 4, Issue 3, March 2017)

is based on random decision errors, kick-back noise and offset voltages.

TABLE 1. COMPARATOR TRUTH TABLE

| CLK | INN | INP | OUTN | OUTP |

|-----|-----|-----|------|------|

| 0   | X   | X   | 1    | 1    |

| 1   | 0   | 0   | 0    | 0    |

| 1   | 0   | 1   | 1    | 0    |

| 1   | 1   | 0   | 0    | 1    |

| 1   | 1   | 1   | 0    | 0    |

In comparator circuits to reduce power consumption the Power gating technique is proposed. In this technique, circuit operates in sleep mode by switching off the current in circuit. Power gating has the benefit that is it measures current (Idd) in the quiescent state.

In this paper the different architectures of double tail comparator is presented. The proposed comparator is designed by using power gating technique. Using this technique power and delay is reduced.

### II. LITERATURE SURVEY OF COMPARATOR

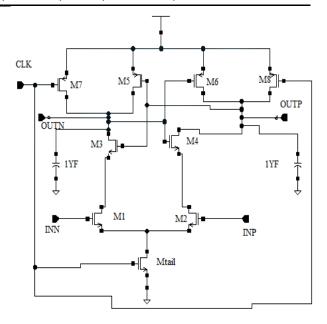

The circuit diagram of the single tail comparator shown in Fig 3. The single tail comparator circuit operation is given below. When CLK=0 the circuit works in reset phase so the Mtail NMOS transistor is in off position and the reset transistors M7 and M8 PMOS transistors are in on position now the output at OUTN and OUTP will be V<sub>DD</sub>. When CLK= V<sub>DD</sub>. Mtail NMOS transistor is in ON position and M7 and M8 PMOS transistors are in OFF position now the OUTN and OUTP output nodes are discharge depending on the INN and INP input voltages. When INP>INN, M5 PMOS transistor will turn ON because of OUTP discharges more speed than OUTN then the output at OUTN=  $V_{DD}$  and output at OUTP=0. When INP<INN, the circuit works in reverse of above operation. When INP voltage> INN voltage, drain current of the transistor M2 causes faster discharge of OUTP compared to OUTN.

Advantages of the single tail comparator are high input impedance, output swing without noise, no static power consumption. The disadvantage is only one current path is available via Mtail NMOS transistor which defines the current for both the differential amplifiers that means a small tail current to keep the differential amplifiers in weak condition so a large current required enabling fast regeneration in the circuit.

Fig 3. Circuit diagram of the single tail comparator

This structure has the power consumption 20.49 nW and circuit delay is 38.83 ps.

## III. CONVENTIONAL COMPARATOR

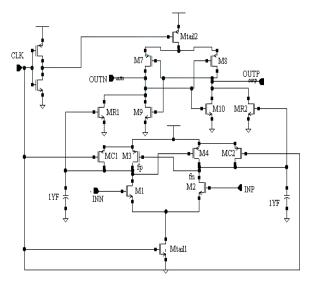

Circuit diagram of the conventional double tail comparator shown in Fig 4. This structure has low static power consumption and operates at lower supply voltages compare to the single tail comparator. The working of this comparator is given below. When CLK=0 the circuit works in reset phase so the Mtail1 NMOS transistor and Mtail2 PMOS transistor are in OFF position and the M3 and M4 PMOS transistors will turn on then the value at nodes fn and fp=  $V_{DD}$ due to this V<sub>DD</sub>. MR1 and MR2 turn ON and discharge the output nodes OUTP and OUTN to the ground. When CLK=  $V_{DD}$ , the circuit works in comparison phase resulting in Mtail1 NMOS transistor and Mtail2 PMOS transistor to switch ON. The M3 and M4 PMOS transistors will turn OFF then the voltages at nodes fn and fp starts to discharge with different charging rates. Due to these discharging transistors MR1 and MR2 are in OFF position so they do not play any role in improving the transconductance.

The circuit power consumption and delay is 59.06 nW and 80.09 ns respectively. The IV section explains how the existing comparator improves performance of double tail comparator.

Website: www.ijeee.in (ISSN: 2348-4748, Volume 4, Issue 3, March 2017)

OUTN MRI M9 MINP TIYF

CLK Mtail2

OUTP

MR1 M9

MY

MY

MY

MY

MINP

TYF

Fig 4. Circuit diagram of conventional Double tail comparator

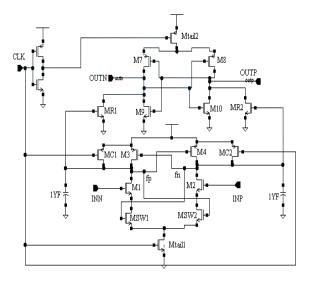

## IV. EXISTING COMPARATOR

Circuit diagram of the existing double tail comparator with static power consumption shown in Fig 5. The existing comparator designed for low voltage applications based on conventional double tail comparator. The main idea of this comparator is to increase Vfn/Vfp ratio and speed up the latch regenerative circuit. MC1 and MC2 PMOS control transistors are connected in parallel to M3 and M4 PMOS transistors. This set up is used to increase speed of the existing comparator. Power consumption of this comparator is 3.468 uW and over all delay is 20.31 ns.

The schematic of existing double tail comparator without static power consumption shown in Fig 6. The working of proposed double tail comparator is given below. When CLK=0 the circuit works in reset phase, Mtail1 NMOS transistor and Mtail2 PMOS transistor are in OFF position and the M3 and M4 PMOS transistors will turn ON then the value at nodes fn and fp= V<sub>DD</sub>, hence MC1 and MC2 PMOS transistors are OFF. Intermediate stage transistors MR1 and MR2 will turn ON because of the value at nodes fn and fp= V<sub>DD</sub>. Consequently the value at OUTN and OUTP=0. When CLK=V<sub>DD</sub> the circuit works in comparison phase so the Mtail1 NMOS transistor and Mtail2 PMOS transistor is in ON position and the transistors M3 and M4 are in OFF state, nodes fn and fp start to discharge at different charging rates depending on the input voltages INN and INP. When INP voltage>INN voltage, M1 NMOS transistor provides less current than M2 NMOS transistor due to this current fn discharges faster than fp.

The disadvantage of this structure is static power consumption whenever the current drawn from VDD to ground through input and Mtail1 transistor. To overcome static power consumption in proposed double tail comparator

two NMOS transistors MSW1 and MSW2 used below the input transistor.

Fig 5. Schematic of the existing Double tail comparator with static power consumption

Fig 6. Schematic of the existing Double tail comparator without static power consumption

The power consumption and delay is reduced compared to the conventional double tail comparator. In comparison phase, both fn and fp nodes discharge to ground in conventional double tail comparator and in reset phase each time they pulled back to  $V_{\rm DD}$ . In proposed double tail comparator one of the node either fn or fp will charge during the reset phase. In the comparison phase, depending on the control transistors one of the node either fn or fp gets discharged. This results in low power consumption. The power consumption of this structure is 135.8 nW and overall delay is 72.4 ps.

Website: www.ijeee.in (ISSN: 2348-4748, Volume 4, Issue 3, March 2017)

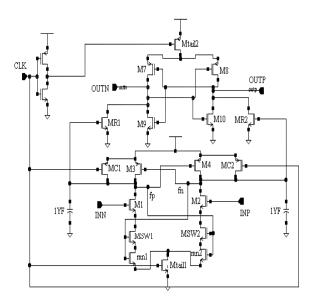

## V. PROPOSED COMPARATOR

Circuit diagram of the proposed double tail comparator shown in Fig 7. Two NMOS transistors mn1 and mn2 are connected in series to MSW1 and MSW2 respectively. This is called power gating technique and it reduces static power consumption. The operation of circuit is same as in section IV. The transistors mn1 and mn2 either have high input voltage or it remains in the OFF state and reduces power consumption. The power consumption of this comparator is 120.2 nW and overall delay is 69 ps.

Fig 7. Circuit diagram of the proposed Double tail comparator

## VI. SIMULATION RESULTS

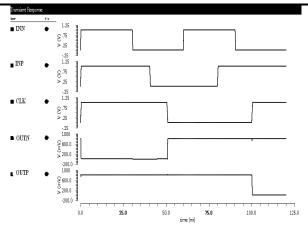

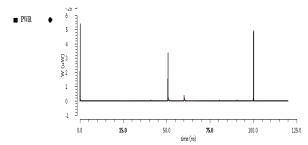

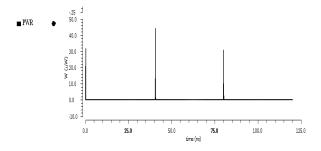

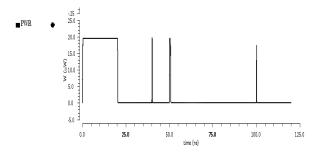

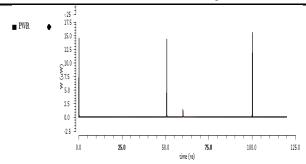

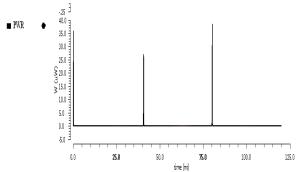

All the circuits are designed by using Cadence Virtuoso tool and simulated in 90 nm CMOS technology with the supply voltage of 0.6V. The output waveform of comparator shown in Fig 8. Power waveform of the single tail comparator is shown in Fig 9. Conventional double tail comparator's power waveform shown in Fig 10. Power waveforms of the existing double tail with static power and without static power are shown in Fig 11 and Fig 12 respectively. Power waveform of the proposed double tail comparator shown in Fig13. Power comparison and delay comparison shown in Table 2 and Table 3 respectively. From this analysis known that the proposed double tail comparator consumed less power and delay also reduced compare to existing and conventional double tail comparator.

Fig 8. Output waveform of comparator

Fig 9. Power waveform of the single tail comparator

Fig 10. Power waveform of the conventional double tail comparator

Fig 11. Power waveform of the existing double tail comparator With static power

Website: www.ijeee.in (ISSN: 2348-4748, Volume 4, Issue 3, March 2017)

Fig. 12. Power waveform of the existing double tail comparator Without static power

Fig 13. Power waveform of the proposed double tail comparator

#### TABLE 2 POWER COMPARISON

| S.no | Comparator type                                      | Power in watts |

|------|------------------------------------------------------|----------------|

| 1    | Conventional double tail comparator                  | 59.66 nW       |

| 2    | Existing double tail comparator with static power    | 3.468 uW       |

| 3    | Existing double tail comparator without static power | 135.8 nW       |

| 4    | Proposed double tail comparator                      | 120.2 nW       |

#### TABLE 3 DELAY COMPARISON

| S.no | Comparator type                                      | Delay (sec) |

|------|------------------------------------------------------|-------------|

| 1    | Conventional double tail comparator                  | 80.09 ns    |

| 2    | Existing double tail comparator with static power    | 20.31 ns    |

| 3    | Existing double tail comparator without static power | 72.4 ps     |

| 4    | Proposed double tail comparator                      | 69 ps       |

## VI. CONCLUSION

Comparison of three double tail comparator circuits being done. All the circuits simulated by using cadence design tools 90nm technology with the supply voltage of 0.6 volt. Using the power gating technique, power consumption and delay is reduced in the proposed double tail comparator. The proposed double tail comparator consumes less power and delay is also reduced compare to previous comparator circuits. Due to additional NMOS transistors there is an increase in area. The comparator circuit used in analog to digital converter structures, sense amplifier, operational amplifier and pre defined amplifier.

#### REFERENCES

- [1]. P. Nuzzo, F. D. Bernardinis, P. Terreni, and G. Van der Plas, "Noise analysis of regenerative comparators for reconfigurable ADC architectures," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 6, pp. 1441–1454, Jul. 2008.

- [2]. P. M. Figueiredo and J. C. Vital, "Kickback noise reduction technique for CMOS latched comapartors," IEEE Trans. Circuits Syst. II, Exp. *Briefs*, vol. 53, no. 7, pp. 541–545, Jul. 2006.s

- [3]. J. He, S. Zhan, D. Chen, and R. J. Geiger, "Analyses of static and dynamic random offset voltages in dynamic comparators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 5, pp. 911–919, May 2009.

- [4]. J. Kim, B. S. Leibowits, J. Ren, and C. J. Madden, "Simulation and analysis of random decision errors in clocked comparators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 8, pp. 1844–1857, Aug. 2009

- [5]. Samanesh Babayan and Reza Lotfi, "Analysis and design oflow-voltage low-power double-tail comparator," IEEE transcations on very large scale integration systems, 2013

- [6]. S. U. Ay, "A sub-1 volt 10-bit supply boosted SAR ADC design in standard CMOS," Int. J. Analog Integr. Circuits Signal Process., vol. 66,no. 2, pp. 213–221, Feb. 2011.

- [7]. B. Goll and H. Zimmermann, "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 11, pp. 810–814, Nov. 2009.