## International Journal of Ethics in Engineering & Management Education Website: www.ijeee.in (ISSN: 2348-4748, Volume 2, Issue 10, October 2015)

## An Ultra Low Leakage High Performance Flipped Voltage Follower Design

## T.NARESH<sup>1</sup> M.Tech in VLSI Sri Indu College of Engineering & Technology

## P. PRASHNATH<sup>2</sup>

Associate Professor Sri Indu College of Engineering & Technology

# K. ASHOK BABU<sup>3</sup> Professor & HOD Dept of EC Sri Indu College of Engineering & Technology

Abstract: Static power consumption has became a serious problem as we tend to area unit moving towards finer technologies. Power consumption is one amongst the highest considerations of VLSI circuit style, for which CMOS is that the primary technology. In bulk CMOS technology the body/substrate terminal of MOS transistor can be used as the fourth terminal. By applying a bias voltage (V SB) at this fourth terminal, V T can be modulated electronically due to the body effect. Body effect enables a variety of effective body biasing techniques. Body biasing is a key enabler of low-power circuit operation and has the potential to enhance the performance of a low voltage analog circuit. A MOS transistor with dynamic body bias technique is known as dynamic threshold MOS (DTMOS) transistor. In paper we Implement Fluffed Voltage Follower was designed using Tanner EDA.

### 1. INTRODUCTION

Out surrounding world is analog in nature. Digital systems require analog to digital conversion at the front of the system and digital to analog conversion at its end. Analog computation and signal processing makes it simpler and faster [2]. Analog signal processing represents the signals as physical quantities like e.g. charge, current, voltage or frequency. These signals are continuous in value and continuous in time. Analog signal processing is most effective when precision is not the major criteria and when massive parallel collective processing of large number of signals that are continuous in time and amplitude is required [3]. In this thesis, we discuss the low voltage analog circuit design. The new smaller size process technologies offer opportunities to operate at higher frequencies consuming less power. For analog circuits, this fact partially applies since it is often the case that additional current is needed to keep the same performance when the power supply voltage is decreased Furthermoren ,for sub-micron technology It would not be possible to use voltage doublers to enhance the circuit performance due to low breakdown voltage of the transistors [4]

Driven by low-power and low-voltage requirements for integrated mixed-signal portable applications, analog signal processing circuits such as four-quadrant analog multipliers are becoming more compact and operate with lower supply voltages. Concentrating on circuit topologies, a circuit cell called "flipped voltage follower" (FVF) has been popularly used for low-voltage design since it needs only a supply voltage of  $V_{TH} \quad \Box V_{eff}$ , where  $V_{TH}$  is the

threshold voltage and  $V_{\it eff}$  (= $V_{\it GS}$  - $V_{\it TH}$ ) is the effective gate voltage.

### 2. THE FLIPPED VOLTAGE FOLLOWER

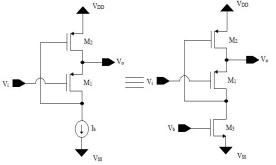

#### 2.1. Source follower

The source follower (common-drain configuration) is shown in Figure 3.1(a). The input signal is applied to the gate and the output is taken from the source. From a largesignal standpoint, the output voltage is equal to the input voltage minus the gate-source voltage. The gate-source voltage consists of two parts: the threshold voltage and the overdrive voltage. If both parts are constant, the resulting output voltage is simply offset from the input, and the small-signal gain would be unity. Therefore, the source follows the gate, and the circuit is also known as a source follower. In practice, the body effect changes the threshold voltage, and the overdrive depends on the drain current, which changes as the output voltage changes unless  $R_L \rightarrow$ ∞. Furthermore, even if the current were exactly constant, the overdrive depends to some extent on the drain-source voltage unless the Early voltage is infinite.

## 2.2 Flipped voltage follower cell

Let us consider the common drain amplifier in Figure commonly used as a voltage buffer. This circuit is also known as a "source follower". If body effect is neglected the circuit follows the input voltage with a dc level shift, i.e.  $V_O \ \Box \ V_i - V_{SG1}$ . Where  $V_{SG1}$  is

the source-to-gate voltage of transistor  $M_1$ . Concerning the large-signal behavior, this circuit is able to sink a large current from the load, but it sourcing capability is limited by the biasing current source  $I_b$ . A drawback of this circuit is that current through transistor  $M_1$  depends on the output current, so that  $V_{SG1}$  is not constant and, hence, for resistive loads, the small and large signal voltage gains are less than unity

## International Journal of Ethics in Engineering & Management Education

Website: www.ijeee.in (ISSN: 2348-4748, Volume 2, Issue 10, October 2015)

Fig1: Flipped voltage follower cell.

The circuit in Fig 1 is another source follower where the current through transistor M1 kept constant independent on output current. It could be described as a follower with shunt feedback. Neglecting the short-channel effect,  $V_{SG1}$  is held constant,

and voltage gains are unity. Unlike the conventional voltage follower, the circuit in Figure 3.3 is able to source a large amount of current, but its sinking capability is limited by the biasing current source  $I_b$ , the large sourcing capability is due to the low impedance at the output node  $(r\ 1\ g_{m1}\ g_{m2}r_1)$ , where  $g_{mi}$  and oi are the trans- conductance and output resistance, respectively. This value is in the order of 20-100.

## 3. DTCMOS

In addition, analysis and development on high potency is crucial to maximise the utilization of moveable device that are most popular numerous functions than within the past. PMIC for prime potency sometimes amendment drastically from linear regulator to switch regulator. however the switch regulator have disadvantage of low potency compared with linear regulator at lightweight load conditions. Therefore, this paper is bestowed the mistreatment of switch regulator at significant load conditions. All power offer device of Mobile appliance should be created stable and numerous DC output voltage of high effectiveness from a unstable DC input power offer.. For that reason, it's used do an influence offer of Switched Mode Power offer(SMPS) methodology rather than an influence offer of typical linear methodology. Therefore, during this paper, the facility provides are designed mistreatment DT-CMOS that is low on resistance than CMOS Switching loss is fixed cause, but conduction loss by on resistance of switch is increased by a output current increased. When output current is increased, conduction loss is increased more than switching loss in high output current. Finally, switch development that have low on-resistance to heighten efficiency of SMPS is essential. In this paper, we proposed available DT-CMOS without high leakage currents in high power supply voltages using this DT-CMOS's concept. The proposed DT-CMOS in this paper can be seen in Fig. 3. When the switch is became ON, the body voltage of the switch MOS is controlled by diode connection CMOS and the threshold

voltage is lowered. When the switch is became OFF, body of CMOS is connected to each the power supply and the ground..

Fig2: DTCMOS Flipped Voltage Follower

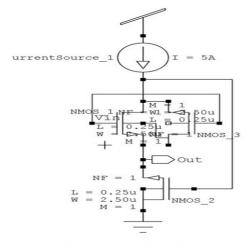

#### Variable body biasing technique:

This is another new leakage reduction technique, which we call the 'Variable body biasing' technique

Self Bias:

If we are connecting a additional substrate voltage to transistor it can be acts like a high threshold transistor so that we can minimize the leakage in it.

Fig3: Variable body biasing Flipped Voltage Follower

## International Journal of Ethics in Engineering & Management Education

Website: www.ijeee.in (ISSN: 2348-4748, Volume 2, Issue 10, October 2015)

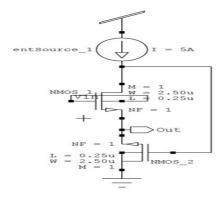

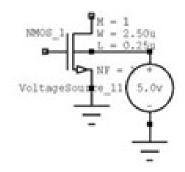

### 4. SIMULATION

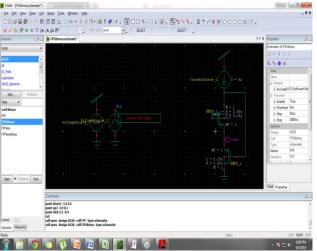

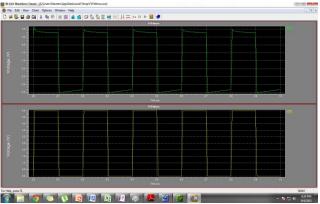

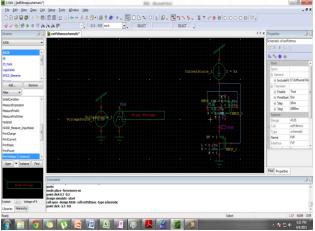

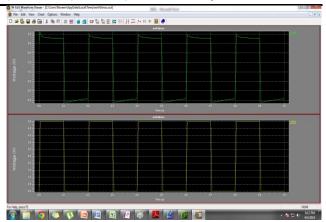

This circuits are designed using S-Edit and Simulated using Tanner T-Spice using TSMC018 Technology.

Fig4: S-EDIT design of DTCMOS Flipped Voltage Follower

Fig5: Simulation of DTCMOS Flipped Voltage Follower

Fig6: S- Edit design Variable body biasing Flipped Voltage Follower

Fig7: Simulation of Variable body biasing Flipped Voltage Follower

## CONCLUSION

In this paper, body effect present in conventional FVF topology has been utilized positively using DTMOS transistor The proposed FVF outperforms the conventional FVF in terms of more symmetrical slew-rate and increased output signal range for which FVF is able to follow input linearly. It is pertinent to mention that these improvements are achieved for same bias current and size of MOS transistor without requiring any additional devices. The important feature of DTMOS is that no extra circuitry is required for body bias voltage generation, as in other body bias techniques. DTMOS approach virtually has no effects on the overall silicon area of proposed FVF and is compatible with standard bulk CMOS process.

### REFERENCES

- [1]. Van, S. & Sanchez, S, "Low voltage analog circuit design techniques: a tutorial" IEICE Transactions analog integrated circuits and systems, EOO-A(2),pp.I-17, 2000.

- [2]. Rajput, S.S. & Jamuar, S.S., "Low Voltage analog circuit design echniques", IEEE Circuits and Systems Magazine, Vol.2, No.1, pp.24-42,2004.

- [3]. Carvajal, R., Ramirez-Angulo, J., Lopez Martin, A., Torralba, A., Galan, J., Carlosena, A., et al., "The flipped voltage follower: A useful cell for low voltage low power circuit design", IEEE Transactions on Circuits and Systems I, Vol. 52, No.7, pp.1276-1279,2005.

- [4]. Haga, Y. and Kale, I., "Bulk-Driven Flipped Voltage Follower", IEEE International Symposium on Circuits and Systems, pp. 2717-2720,2009.

- [5]. Lujan, c.1., Torralba, A., Carvajal, R.G. & Ramirez-Angulo, J., "Highly linear voltage follower based on local feedback and cascode transistor with dynamic biasing", IEE Electronics Letters, VoL47, No.4, pp.244-246, 2011.

- [6]. Blakiewicz, G., "Output-capacitorless low-dropout regulator using a cascoded flipped voltage follower", IET Circuits Devices and systems, Vol.5, No.5, pp.418-423, 2011.

- [7]. Ramirez-Angulo, J., Gupta, S., Padilla, I., Carvajal, R. G., Torralba, A., Jimenez, M., et al., "Comparison of conventional and new flipped voltage structures with increased input/output signal swing & current sourcing/sinking capabilities", 48<sup>th</sup> IEEE midwest symposium on circuits and systems, Vol.2, pp.1 151-1 154, 2005.

- [8] RamIrez-Angulo, J., Lopez-Martm, AJ., Carvajal, R.G., Torralba, A., and Jimenez, M., "Simple class-AB voltage follower with slew rate and bandwidth enhancement and no extra static power or supply

## International Journal of Ethics in Engineering & Management Education

Website: www.ijeee.in (ISSN: 2348-4748, Volume 2, Issue 10, October 2015)

- requirements", IEE Electronics Letters, VoL42, No.14, pp.784-785, 2006

- [9]. MJ. Wong, M. Ho and K.N. Leung, "High slew-rate voltage follower based on double-sided dynamic biasing", IEE Electronics Letters, VoL46, No.12, pp.824 - 825, 2010.

- [10]. Yannis P. Tsividis and Donald L. Fraser, Jr., "Harmonic Distortion in Single-Channel MOS Integrated Circuits", IEEE Journal of Solid-State Circuits, Vol.SC-16, No.6,pp.694-702, 1981.

- [11]. Niranjan, V., et.aL, "Body Biasing-A circuit level approach to reduce leakage in Low power CMOS circuits", Journal of Active and Passive Electronic Devices, VoL6, No.1-2,pp.89-99, 2011.

- [12] C. J. B. Fayomi, M. Sawan, G.W. Roberts, "Reliable Circuit Techniques for Low- Voltage Analog Design in Deep Submicron Standard CMOS: A Tutorial", Analog Integrated Circuits and Signal Processing, Vol.39, No.1, pp.21 - 38, 2004.

- [13] Niranjan, V. et.aL, "Triple Well Subthreshold CMOS Logic Using Body-bias Technique", Proceedings 2013-IEEE International Conference on Signal Processing, Computing and Control, September 2013.

- [14] Assaderaghi, F., Sinitsky, D.,Parke S.A., et. al.,"Dynamic threshold voltage MOSFET (DTMOS) for ultra low voltage VLSI" IEEE Transactions on Electron Devices, VoL44, No.3, pp.414-422,1997.

- [15] X. Zhu and Y. Sun, "Low-distortion low-voltage operational transnconductance amplifier" IEE Electronics Letters, Vol.44, No.25, pp.1434 - 1436,2008. 150

#### **About the Authors:**

T.NARESH<sup>1</sup> Perusing M.Tech in VLSI from Sri Indu College of Engineering & Technology.

P. PRASHANTH<sup>2</sup>, Working as a Associate Professor in ECE Dept. in Sri Indu College of Engineering & Technology.

**K. ASHOK BABU**<sup>3</sup>, Currently working as professor & HOD Dept of ECE in Sri Indu College of Engineering & Technology.